AI · SOC芯片设计

标准接口的IP和SoC的数字功能验证

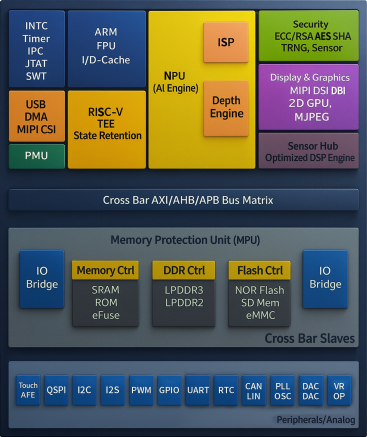

RISC-V+ARM双核架构

- ARM Cortex完善生态系统

- AP CPU高性能+FPU+Cache

- RISC-V开源指令集自主可控

- 双核CPU无缝协作

- 高性能、低功耗、低延时

AI引擎、语音/视觉加速器

- 定制AI引擎,优化提升算力

- 定制图像处理ISP

- 定制深度计算引擎

- 低功耗边缘语音识别

- 高性能视觉芯片

超低功耗

- 内置电源管理模块PMU

- 灵活可配置的功耗模式切换

- 超低的待机功耗

- 支持CPU retention, DVFS等先进技术

丰富存储配置

- 支持LPDDR内存

- 支持eMMC主流存储

- 支持Nor Flash

- 支持存储器数据加密

- 支持SD memory

- 支持eFlash / NandFlash

安全

- 加密硬件IP (ECC,RSA,AES)

- Root of Trust安全启动

- 对接EAL4+的安全规格

- MPU内存访问管理

显示/图像/音频

- 内置显示模块,支持MIPI

- 2D图像加速,支持GUI设计

- MJPEG视频录音音频解码

超低功耗IoT Sensor Hub

- 针对IoT定制的DSP引擎

- 低功耗传感器数据采集

- 高性能医疗传感器芯片

- 高安全性汽车电子传感器

低功耗高速通信接口

- 丰富的MCU外设接口

- 内置ADC/DAC等高性能模拟IP

- IoT无线连接:WIFI/BT/BLE

产品价值

芯片设计异构仿真加速器

面向高校科研与企业研发场景,聚焦解决数字 SoC 设计中验证与仿真周期长、算力消耗大的核心瓶颈。在典型 SoC 项目中,约 70% 的时间与资源投入在验证阶段,加速能力直接决定研发效率。该产品融合国产 EDA 工具与 AI+EDA 平台,采用 CPU、GPU、FPGA 等异构算力协同架构,支持软件算法与硬件加速的混合仿真模式,并与 IP / VIP 平台深度协同,可稳定支撑超千万门级复杂 SoC 的完整时序仿真与验证,为科研与工程研发提供高效、可扩展的加速能力。

了解详情

基于AI的

集成电路设计超融合一体机

是一套面向高校的 AI 融合集成电路 EDA 实训平台,集成工程化课程体系、产业级项目案例、企业级 IC 设计与仿真环境以及教学管理与 AI 辅助教学能力。平台依托统一的高性能计算与 GPU 算力,构建稳定一致的设计环境,完整覆盖集成电路前端设计、验证、后端实现与版图流程,真实还原产业级开发路径。通过项目制教学,引导学生在真实工程场景中完成从设计概念到 GDSII 的全过程,帮助高校高效开展集成电路全流程教学与工程型人才培养。

了解详情

AI智算赋能IC

让AI加速 EDA、加速IP 、加速芯片设计的每一个环节

EDA+AI(DeepChip)

降低芯片设计用户获取AI门槛,让大模型更快产生业务价值,在芯片设计复杂度激增的今天,首次流片成功率已从两年前的24%骤降至14%。每一次流片失败都意味着数百万美元的损失和错失市场窗口的风险。面对这一行业危机,DeepChip以独特的解决方案脱颖而出。

核心优势

- 1000+成功流片的AI智慧

- 行业独有的千次流片知识库

- 基于1000+真实成功流片案例训练的专业AI模型

- 涵盖全工艺节点的设计经验

- 累积超过50万小时的实际芯片设计数据

- 包含数字芯片、模拟芯片、射频芯片、数模混合芯片等全领域芯片架构

IP+AI(DeepIP)

DeepIP是启芯宸光面向芯片设计核心环节打造的智能化能力模块。

通过 AI 对 IP 规格、接口、参数与设计约束的深度理解,系统能够显著降低 IP 使用门槛,缩短集成与适配周期,让工程团队在更短时间内完成高质量设计。

核心优势

- 系统能够对 IP 文档等关键信息进行结构化解析

- AI能够辅助完成 IP 参数选择与配置建议,提出设计引导

- 对于复杂系统,能够提供IP集成与系统级协同

- 统一的智能生成与管理机制,使得设计更规范可维护

- 面向教学与企业的双场景适配